トップページ

研究活動

研究活動

研究チーム紹介

研究チーム紹介

プロセッサ研究チーム

プロセッサ研究チーム

プロセッサ研究チーム

English

チームプリンシパル 佐野 健太郎

(さの けんたろう) kentaro.sano[at]riken.jp (拠点:神戸)

kentaro.sano[at]riken.jp (拠点:神戸)- Emailの[at]は@にご変更ください。

- 2000

- 東北大学大学院情報科学研究科情報基礎科学専攻修了

- 2000

- 東北大学大学院工学研究科助手

- 2001

- 東北大学大学院情報科学研究科情報基礎科学専攻助手

- 2005

- 東北大学大学院情報科学研究科情報基礎科学専攻助教授(2007年より准教授)

- 2006

- インペリアルカレッジロンドン客員研究員

- 2017

- 理化学研究所 計算科学研究機構(AICS)(現在:計算科学研究センターR-CCS)プロセッサ研究チーム チームリーダー(現職)

- 2019

- 東北大学大学院情報科学研究科 客員教授

- 2024

- 理化学研究所 計算科学研究センター(R-CCS)AI for Scienceプラットフォーム部門 次世代AIデバイス開発研究ユニット ユニットリーダー(現職)

- 2025

- 理化学研究所計算科学研究センター(R-CCS)次世代計算基盤開発部門 次世代計算基盤システム開発ユニット ユニットリーダー(現職)

キーワード

- 計算機アーキテクチャ

- 問題特化型ハードウェア設計

- ハードウェアアルゴリズム

- 次世代AIデバイス

- 誤り耐性量子計算機

研究概要

ムーアの法則と呼ばれる半導体微細化加工技術スケーリングの減速や、パッケージング技術やメモリ技術の進展等を考慮しながら、以下のような、低電力で高性能処理の計算機アーキテクチャを研究します。

- HPCやAIのための次世代計算機アーキテクチャの探求

- アプリケーションに最適化した問題特化型の計算機アーキテクチャの探求。例えば、量子誤り訂正ハードウェアや、放射光施設の検出センサー近傍処理ハードウェア

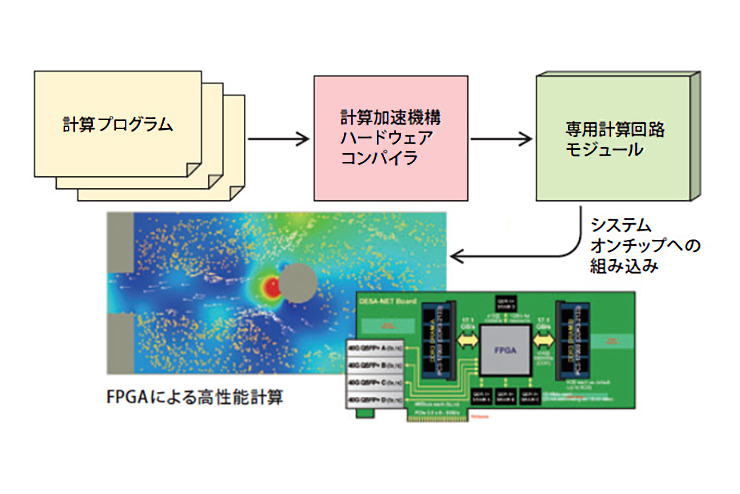

- 高性能な問題特化型計算機アーキテクチャを研究開発するためのシステム探求。特に、FPGAクラスタシステム

主な研究成果

HPCおよびAIのための粗粒度回路再構成アレイ(CGRA)

データフロー計算モデルに基づくアーキテクチャであるCGRAの研究を行っています。これまで、トロント大学との共同研究を通じて、基本アーキテクチャである理研CGRAの開発と設計空間探索を行いました。

誤り耐性量子計算機のための、量子誤り訂正ハードウェア

物理量子ビットや測定のエラーを克服する誤り耐性量子計算機FTQC (Fault-tolerant quantum computer)の実現が求められています。当チームでは、表現符号の誤り訂正処理(エラーデコード)を低遅延かつ高スループットで行うハードウェアを研究開発しており、これまで、その試作設計と評価を行いました。

問題特化型高性能計算機アーキテクチャ研究プラットフォーム

半導体微細化による電力効率向上が困難となる中、問題特化型の計算機アーキテクチャが注目されています。そのために、FPGAクラスタESSPER (Elastic and Scalable System for High-Performance Reconfigurable Computing)を開発しました。また、パケット交換網上に任意のトポロジを構築可能な仮想回線交換網 VCSNを開発しました。

FPGAによる問題特化型計算ハードウェアの設計および実装

データ圧縮アルゴリズムおよびハードウェア

計算処理のボトルネックとなり大きな割合の電力を消費するデータ移動の問題を解決するために、数値データストリームをメモリに貯めることなくその場で可逆圧縮可能な高スループットのハードウェア圧縮器を開発しました。

主要論文

- Franck Cappello, Sheng Di, Robert Underwood, Dingwen Tao, Jon Calhoun, Yoshii Kazutomo, Kento Sato, Amarjit Singh, Luc Giraud, Emmanuel Agullo, Xavier Yepes, Mario Acosta, Sian Jin, Jiannan Tian, Frédéric Vivien, Boyuan Zhang, Kentaro Sano, Tomohiro Ueno, Thomas Grützmacher, Hartwig Anzt

"Multifacets of lossy compression for scientific data in the Joint-Laboratory of Extreme Scale Computing"

FGCS (Elsevier Future Generation Computer Systems), Vol.163, DOI:10.1016/j.future.2024.05.022, 2024. - Juan Miguel de Haro Ruiz, Carlos Alvarez Martınez, Daniel Jimenez-Gonzalez, Xavier Martorell, Tomohiro Ueno, Kentaro Sano, Burkhard Ringlein, Francois Abel, Beat Weiss

"Automated parallel execution of distributed task graphs with FPGA clusters"

FGCS (Elsevier Future Generation Computer Systems), Vol.160, Issue C, pp.808-824, DOI:10.1016/j.future.2024.06.041, 2024. - Tomohiro Ueno, Emanuele Del Sozzo, Kentaro Sano

"Flexible Systolic Array Platform on Virtual 2-D Multi-FPGA Plane"

Proceedings of HPC Asia 2024: The International Conference on High Performance Computing in Asia-Pacific Region, pp.84–94, DOI: 10.1145/3635035.3637285, Jan 25–27, 2024. - Emanuele Del Sozzo, Xinyuan Wang, Boma Adhi, Carlos Cortes, Jason Anderson, Kentaro Sano

"Exploration of Trade-offs Between General-Purpose and Specialized Processing Elements in HPC-Oriented CGRA"

Proceedings of IEEE International Parallel & Distributed Processing Symposium (IPDPS), pp.668-680, DOI: 10.1109/IPDPS57955.2024.00065., 2024. - Emanuele Del Sozzo, Davide Conficconi, Kentaro Sano

"Across Time and Space: Senju’s Approach for Scaling Iterative Stencil Loop Accelerators on Single and Multiple FPGAs"

FPT Journal Track with ACM Transactions on Reconfigurable Technology and Systems (TRETS), Vol.17, Issue.2, Article No.28, pp.1-33, DOI: 10.1145/3634920, 2024. - Philippos Papaphilippou, Kentaro Sano, Boma A. Adhi, and Wayne Luk

"Experimental survey of FPGA-based monolithic switches and a novel queue balancer"

IEEE Transactions on Parallel and Distributed Systems (TPDS), Vol.34, no.5, pp.1621-1634, DOI: 10.1109/TPDS.2023.3244589, 2023. - Kentaro Sano, Atsushi Koshiba, Takaaki Miyajima, and Tomohiro Ueno

"ESSPER: Elastic and Scalable FPGA-Cluster System for High-Performance Reconfigurable Computing with Supercomputer Fugaku"

Proceedings of HPC Asia2023, pp.140-150, DOI: 10.1145/3578178.3579341, 2023. - Tomohiro Ueno and Kentaro Sano

"VCSN: Virtual Circuit-Switching Network for Flexible and Simple-to-Operate Communication in HPC FPGA Cluster"

ACM Transactions on Reconfigurable Technology and Systems (TRETS), Vol.16, Issue.2, Article No.25, pp.1-32, DOI: 10.1145/3579848, 2023. - Boma Adhi, Carlos Cortes, Yiyu Tan, Takuya Kojima, Artur Podobas, and Kentaro Sano

"The Cost of Flexibility: Embedded versus Discrete Routers in CGRAs for HPC"

Proceedings of IEEE Cluster Conference (CLUSTER), pp.347-356, DOI: 10.1109/CLUSTER51413.2022.00046, Sep 6-9, 2022. - Artur Podobas, Kentaro Sano, and Satoshi Matsuoka

"A Survey on Coarse-Grained Reconfigurable Architectures from a Performance Perspective"

IEEE Access, Vol.8, pp.146719-146743, DOI:10.1109/ACCESS.2020.3012084, 2020.