トップページ

研究活動

研究活動

研究チーム紹介

研究チーム紹介

次世代高性能アーキテクチャ研究チーム

次世代高性能アーキテクチャ研究チーム

次世代高性能アーキテクチャ研究チーム

English

チームプリンシパル 近藤 正章

(こんどう まさあき) masaaki.kondo[at]riken.jp (拠点:神戸)

masaaki.kondo[at]riken.jp (拠点:神戸)- Emailの[at]は@にご変更ください。

- 2003

- 東京大学大学院工学系研究科先端学際工学専攻修了 博士(工学)

- 2003

- 科学技術振興機構戦略的創造研究推進事業研究員

- 2004

- 東京大学先端科学技術研究センター特任助手

- 2007

- 東京大学先端科学技術研究センター特任准教授

- 2008

- 電気通信大学大学院情報システム学研究科准教授

- 2013

- 東京大学大学院情報理工学系研究科准教授

- 2014

- 理化学研究所計算科学研究センター(R-CCS)フラッグシップ2020プロジェクトアーキテクチャ開発チーム 客員研究員

- 2018

- 理化学研究所計算科学研究センター(R-CCS)次世代高性能アーキテクチャ研究チーム チームリーダー(現職)

- 2021

- 慶應義塾大学理工学部情報工学科教授(現職)

- 2025

- 理化学研究所計算科学研究センター(R-CCS)次世代計算基盤開発部門 部門長(現職)

キーワード

- 計算機アーキテクチャ

- スーパーコンピュータ

- 並列・分散処理

- 非ノイマン型アーキテクチャ

- 計算アクセラレータ

研究概要

「京」や「富岳」といった近年の計算機システムの高速化のトレンドは、ムーアの法則として知られるトランジスタ微細化により支えられてきました。しかし、ムーアの法則も近い将来に終焉を迎えると考えられており、性能と電力効率を将来にわたりスケール可能な高性能計算機システムの実現は、今後取り組むべき最も重要な課題の一つです。当研究チームでは、「京」・「富岳」をベースとしつつ、その改良を含むソフトウェアとハードウェアによって構成される次世代の高性能計算機アーキテクチャと、エクサスケールシステムの電力効率の改善に関する研究・開発に取り組んでいます。特に、デバイスの進化を踏まえたシストリックアレイやニューロモーフィック計算といった非ノイマン型計算機、次世代の不揮発性メモリやさまざまな種類の演算加速機構と汎用プロセッサを高度に融合可能なアーキテクチャ、機械学習の計算を加速することによるシミュレーションの高度化、量子計算と古典計算のそれぞれの利点を生かしたハイブリッドな計算機アーキテクチャなど、次世代アーキテクチャやそれらを活かすアルゴリズムの研究と、「京」・「富岳」上でのコデザイン評価を主軸に研究を行っています。

主な研究成果

次世代高性能計算機システムの電力管理手法の開発

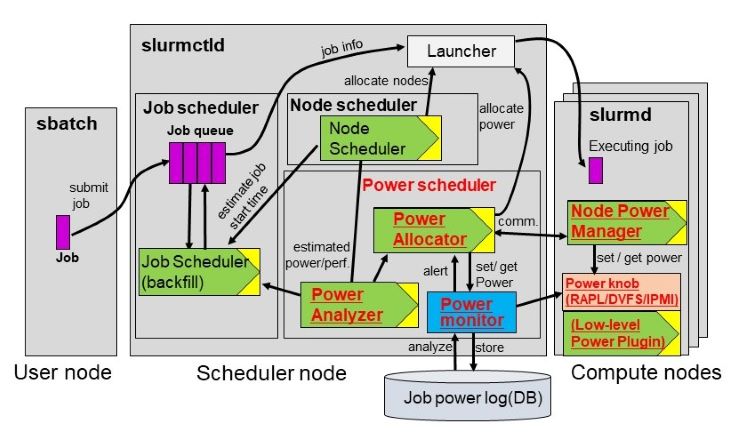

エクサスケール級や、さらに次世代の高性能計算システムでは、消費電力がシステム設計や実効性能を制約する最大の要因になると考えられています。その解決策の一つとして、ピーク消費電力が電力制約を超過することを許し、ハードウェアがもつ電力性能の調整ノブを適応的に制御することで実効電力を制約以下に抑えるシステム形態が提唱されています。そのようなシステムでは、利用可能な全ハードウェア資源を使い切るのではなく、限られた電力資源を計算・記憶・通信という要素間、あるいは特徴の異なるジョブ間で適応的に配分することが重要です。このために、アプリケーションの特性と運用状況に合わせた電力性能ノブ最適化ツールと、電力を含めたシステムの資源管理ソフトウェアを開発中です。例えば、計算ノード間の電力のばらつきに対応したノード間電力配分最適化をすると、同一の電力制約下で最大5.4倍の性能向上が得られることもわかっています。また、ジョブ間で電力資源の配分が可能なジョブスケジューラを、世界的に広く利用されているSlurm Resource Managerをベースに開発し、1000ノード規模の計算機クラスタ環境で動作させることに成功しています。

主要論文

- Tsukada, M, Kondo, M., and Matsutani, H.:

OS-ELM-FPGA: An FPGA-Based Online Sequential Unsupervised Anomaly Detector"

The 16th International Workshop on Algorithms, Models and Tools for Parallel Computing on Heterogeneous Platforms (HeteroPar'18). (2018).

- Sakamoto, R., Patki, T., Cao, T., Kondo, M., Inoue, K., Ueda, M., Ellsworth, D., Rountree, B., and Martin Schulz.:

Analyzing Resource Trade-offs in Hardware Overprovisioned Supercomputers"

32nd IEEE International Parallel & Distributed Processing Symposium (IPDPS2018), 10 pages. (2018).

- Wada, Y., He, Y., Cao, T., and Kondo, M.:

"A Power Management Framework with Simple DSL for Automatic Power-Performance Optimization on Power-Constrained HPC Systems"

SupercomputingAsia 2018 (SCA18), 20 pages. (2018).

- Shresthamali, S., Kondo, M., and Nakamura, H.:

"Adaptive Power Management in Solar Energy Harvesting Sensor Node using Reinforcement Learning"

ACM Transactions on Embedded Computing Systems, Vol.16, No.5s, pp.181:1-181:21. (2017).

- Sakamoto, R., Takata, R., Ishii, J., Kondo, M., Nakamura, H., Ohkubo, T., Kojima, T., and Amano, H.:

"The Design and Implementation of Scalable Deep Neural Network Accelerator Cores"

IEEE 11th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC-17), 8 pages. (2017).

- Sakamoto, R., Cao, T., Kondo, M., Inoue, K., Ueda, M., Patki, T., Ellsworth, D., Rountree, B., and Schulz, M.:

"Production Hardware Overprovisioning: Real-world Performance Optimization using an Extensible Power-aware Resource Management Framework"

31st IEEE International Parallel & Distributed Processing Symposium (IPDPS2017). 10 pages. (2017).

- Cao, T., Huang, W., He, Y., and Kondo, M.:

"Cooling-Aware Job Scheduling and Node Allocation for Overprovisioned HPC Systems"

31st IEEE International Parallel & Distributed Processing Symposium (IPDPS2017), 10pages. (2017).

- Ohkubo, T., Tanaka, T., Sakamoto, T., Kondo, M., and Amano, H.:

"NAMACHA: A Software Development Environment for a Multi-Chip Convolutional Network Accelerator"

32nd International Conference on Computers and Their Applications (CATA'17). (2017).

- He, Y., Kondo, M., Nakada, T., Sasaki, H., Miwa, S., and Nakamura, H.:

"A Runtime Multi-Optimization Framework to Realize Energy Efficient Networks-on-Chip"

IEICE Transactions on Information and Systems, Vol.E99-D, No.12, pp.2881-2890. (2016).

- Inadomi, Y., Patki, T., Inoue, K., Aoyagi, M., Rountree, B., Schulz, M., Lowenthal, D., Wada, Y., Fukazawa, K., Ueda, M., Kondo, M., and Miyoshi, I.:

"Analyzing and Mitigating the Impact of Manufacturing Variability in Power-Constrained Supercomputing"

The International Conference for High Performance Computing, Networking, Storage and Analysis (SC15), 2 pages. (2015)