This study was carried out for RIKEN by

## Special Study

## Analysis of the Characteristics and Development Trends of the Next-Generation of Supercomputers in Foreign Countries

Earl C. Joseph, Ph.D. Robert Sorensen Steve Conway Kevin Monroe

## **IDC OPINION**

Leadership-class supercomputers have contributed enormously to advances in fundamental and applied science, national security, and the quality of life. Advances made possible by this class of supercomputers have been instrumental for better predicting severe weather and earthquakes that can devastate lives and property, for designing new materials used in products, for making new energy sources pragmatic, for developing and testing methodologies to handle "big data," and for many more beneficial uses.

The broad range of leadership-class supercomputers examined during this study make it clear that there are a number of national programs planned and already in place to not only build pre-exascale systems to meet many of today's most aggressive research agendas but to also develop the hardware and software necessary to produce sustained exascale systems in the 2020 timeframe and beyond. Although our studies indicate that there is no single technology strategy that will emerge as the ideal, it is satisfying to note that the wide range of innovative and forward leaning efforts going on around the world almost certainly ensures that the push toward more capable leadership-class supercomputers will be successful.

IDC analysts recognize, however, that for almost every HPC development project examined here, the current effort within each organization is only their latest step in a long history of HPC progress and use. As such, IDC analysts assess that a leading-edge supercomputer development and user facility must be continually involved in the exploration of new system technology, or risk falling behind those consistently committed to the acquisition and use of leadership-class systems. IDC analysts believe that the cost of missing even one generation of HPC development could cause substantial difficulties for any facility looking to maintain a world-class HPC-based research capability.

Looking at the strengths and weaknesses in exascale plans and capabilities of different countries:

- The U.S. has multiple programs, strong funding and many HPC vendors, but has to deal with changing federal support, a major legacy technology burden, and a growing HPC labor shortage.

- Europe has strong software programs and a few hardware efforts, plus EU funding and support appears to be growing, and they have Bull, but they have to deal with 28 different countries and a weak investment community.

- China has had major funding support, has installed many very large systems, and is developing its own core technologies, but has a smaller user base, many different custom systems and currently is experiencing low utilization of its largest computers.

IDC analysts stress that that time and again, successful national leadership-class supercomputer facilities have played an important role in underwriting new developments in hardware and software that prove to be applicable to a wide range of scientific, engineering, and industrial disciplines. At the same time, these programs provide significant support for their nations' domestic HPC supplier ecosystem, helping them remain at the forefront in global HPC technology developments. IDC believes that countries that fail to fund development of these future leadership-class supercomputers run a high risk of falling behind other highly developed countries in scientific innovation, with later harmful consequences for their national economies.

Finally, the HPC sector is currently undergoing a significant transition away from being limited to a relatively small HPC user base centered on scientific modeling and simulation applications and is rapidly embracing a broad span of new use cases. Some of these new uses will employ traditional HPC hardware and software. Many of the more innovative, forward leaning, and rapidly growing sectors could require the development of a wide range of new HPC technology involving new processor designs in both the CPU and GPU area, deeper memory schemes, more capable interconnects, and the wide range of associated systems and application software needed to provide a fully capable solution. Some of these emerging HPC-relevant sectors that IDC has identified include:

- A rapidly growing base of big data applications with complex requirements that can only be managed on HPC platforms in areas such as precision medicine, the financial sector, and cyber security.

- New demands for computational performance in data intensive Internet of Things applications as well as those that merge significant computational capabilities with mobile applications, such as voice or image recognition on smart phones.

- The profusion of new options for HPC in the cloud that will almost certainly bring a new host of

users and applications to the HPC world as technical barriers to entry and the cost of running

some HPC jobs in the cloud become less daunting barriers across a wide range of industrial

sectors, especially for a number of small and medium business.

- Breakthroughs in deep learning and other cognitive computing areas that will drive the need for new HPC designs and expand the boundaries of new programming paradigms,

## **EXECUTIVE SUMMARY**

This IDC report summarizes a number of leadership-class supercomputer developments on-going and planned within the next five years at leading supercomputer sites around the world. In essence, it is an attempt to capture in significant detail, supported by technical information, some of the most important -- and technologically forward learning -- developments in supercomputers from today out to 2020 and beyond.

There are a number of major leadership-class HPCs in the planning and development stage targeted for deployment between 2016 and 2020. In addition to Japan, such development is under way across a wide range of major HPC suppliers and regions including China, the EU, and the United States.

- Most of these systems are pre-exascale designs: systems that will underwrite much of the technology critical to the development of the hardware and software necessary to support the spate of exascale systems planned for the 2020 to 2022 time-frame.

- As such, the bulk of the systems planned for the next four years target a peak performance capability between 10 and 300 teraflops, with the bulk of the lower-end systems closer to completion this year or the next, while higher performance systems are targeted for completion closer to 2020.

### Many Different Architectures Are Being Researched

There are a wide range of different architectural design paths to an exascale system.

- Some projects are looking to partner with a commercial vendor, such as Cray or IBM, to help them develop a leadership-class system that is in keeping with the overall product offerings of their commercial partner, such as the Cheyenne SGI system at NCAR.

- Others, such as NUDT's Tianhe-2 A group in China, are essentially looking to custom-build a system that likely will be produced in very limited quantiles, be used primarily in domestic markets, and developed with little expectation of eventual commercialization.

- In addition, it is clear that there is no agreed upon architectural scheme for these pre-exascale systems.

## GPU and Accelerators Will be in a Number of Special Purpose Systems

But these designs in most cases will be less general purpose than designs that use a single processor type. A number of large sites around the world have been conducting studies to determine which codes fit best on which type of architectures. For the most general purpose environments, the use of a standard common CPU provides the broadest solution to the largest number of diverse researchers. Systems with a large percentage of GPUs are useful for specific types of codes, but result in more special purpose designs.

## Power Consumption is a Major Concern

Concerns about power consumption and related efficiencies are keeping total power needs for preexascale system generally below 30 MW.

In addition, many designers are looking for ways to better control the real-time power draw of their systems by using advanced techniques to shut down power-hungry portions of their systems when not in use during a particular job or even portion of a job.

## Most Aren't Focused on Only Peak Performance

IDC analysts assess that designers, developers, and users of pre-exascale systems are not generally concerned with the theoretical peak computation performance of their new systems.

Instead IDC analysts note that there is an increased emphasis on determining the ability of a new system to deliver a sustained performance - one that captures the ability of a system's overall compute, memory, interconnect, and storage infrastructure to execute an end-to end task - over one that stresses pure computationally capability.

## A Wide Mix in Budgets for Developing and Building These Exascale Systems

Pre-exascale designers are operating under a wide range of budgets from a low of \$25 million to well over ten times that amount.

- Some of the most expensive pre-exascale systems such as the most technologically, aggressive one-off systems - are projected to cost \$250 million or more. These systems represent some of the most advanced HPC developments in the world, and include significant non-recoverable engineering (NRE) costs.

- Others, primarily those that are one step behind the leading-edge of performance, generally

are looking at budgets an order of magnitude less. Many of these systems have less

aggressive NRE requirements and instead rely primarily on hardware and software technology

supplied by their vendor partners.

### Ease-of-use Will Require Major Investments

IDC analysts assess that for the most part, the leadership-class supercomputers under development have accounted well for the fundamental ease of use features that they will need for their best possible operation.

This is not surprising as the increasingly higher costs of such systems almost automatically justify significant pre-planning and designer/user collaboration not just within the specific project, but more commonly across projects, some of which transcend bureaucratic as well as national borders.

#### Exciting New Hardware Trends

Notable hardware trends that emerged from this study included:

- There is a wide range of pre-exascale processors and related GPU accelerators being considered for inclusion in the various systems.

- The overarching trend in pre-exascale design is toward more memory, more SSDs, and the use of additional memory accelerators, such as burst buffers or high bandwidth memory packages as a way to deal with the increasing need for higher bandwidth and lower latency memory systems.

- For most of the systems that will be delivered soon, designers are opting for either InfiniBand, Intel OmniPath, or in a few cases, a custom in-house interconnect scheme.

- Leadership class supercomputer designs have overall storage requirements that are moving well into the 100PB range in the next few years.

#### Interesting New Software Trends

Notable software trends that emerged from this study included:

- Linux, in its many variants, has become the stock operating system for most leadership-class supercomputer, and IDC analysts assess that this will be the case for at least the next five years.

- Lustre and GPFS are and likely will continue to be the major file system software for leadership-class supercomputers for at least the next five years.

- There is modest attention being paid to non-traditional HPC software that IDC analysts expect will become increasingly important in the next few years, such as for big data infrastructures built around the Hadoop/Apache Spark (or other alternative) ecosystem and for virtualization schemes such as Docker.

#### Partnerships for Developing These Systems

Analysis of the major R&D plans and partnerships for most of the leadership-class supercomputers studied offers a few key insights worth noting.

- Some, such as those in the US DOE, are seeking to not only meet their near-term computational requirements but are also committing significant NRE to help lay the hardware and software foundation for exascale systems that are scheduled for completion in the 2020 to 2022 time-frame.

- Others are targeted more toward near-term computing requirements that do not include any significant commitment of NRE funding, such as the Swiss Piz Daint which instead looked to partner with a commercial vendor (Cray) to meet its less aggressive, albeit no less important, computational requirements with more traditional HPC architectures.

- Finally, there are some that are focused primarily as research systems, built in limited quantities, more for their value as HPC research machines than as production systems.

Partnerships are becoming a fundamental reality of leadership-class HPC development. There were a wide range of partnership types across the projects IDC examined.

- Some like the CORAL effort within the US DOE look to use the combined HPC hardware and software expertise of partnership members to examine a number of alternative HPC technologies while still meeting the particular mission requirements of each individual organization.

- Other partnerships look instead to a provide a rationalized development and research program across a number of sites to ensure that a range of design options are explored in a systematized fashion.

Likewise, almost all major leadership-class projects involve some committed partnership with one or more commercial vendors, be it at the component, system, or software level. Such partnerships can yield substantial benefits for both parties.

- The procuring lab is able to help design and purchase technology in cooperation with some of the leading HPC suppliers in the world that might never be available on the commercial market,

- At the same time, vendors benefit from a first-hand partnership with some most forwardleaning thinkers in HPC design, helping them better develop technology that can then be used in their wider product lines bound for the commercial sector.

## Many National Programs Have Developed to Support These Efforts

The broad range of leadership-class supercomputers examined during this study make it clear that there are a number of national programs planned and already in place to not only build pre-exascale

systems to meet many of today's most aggressive research agendas but to also develop the hardware and software necessary to produce sustained exascale system in the 2020 timeframe and beyond.

Although our studies indicate that no single technology development plan will emerge as the dominant scheme the wide range of innovative and forward leaning efforts going on around the world almost certainly ensures that the push towards more capable, powerful leadershipclass supercomputers will be successful.

IDC analysts stress, however, that for almost every HPC development project examined here, the current effort within each organization is only their latest step in a long history of HPC development and use.

- A leading-edge supercomputer user facility must be continually involved in the development of new system on a timely basis or risk falling behind those committed to the regular, periodic acquisition and use of leadership-class HPCs.

- The cost of missing even one generation of HPC development could cause considerable difficulties for any facility looking to maintain a world-class HPC-based research capability.

Finally, time and again, successful national leadership-class supercomputer facilities have played an important role in driving HPC-based developments by underwriting new capabilities in hardware and software applicable to a wide range of scientific, engineering, and industrial disciplines.

- At the same time, these programs provide significant support for the domestic HPC supplier ecosystem to remain at the forefront of global technology developments.

- IDC believes that countries that fail to fund development of these future leadership-class supercomputers run a high risk of falling behind other highly developed countries in scientific innovation, with later harmful consequences for their national economies.

# *Strengths and Weaknesses in Exascale Plans and Capabilities of Different Countries*

Looking at the strengths and weaknesses in exascale plans and capabilities of different countries:

- The U.S. has multiple programs, strong funding and many HPC vendors, but has to deal with changing federal support, a major legacy technology burden, and a growing HPC labor shortage.

- Europe has strong software programs and a few hardware efforts, plus EU funding and support appears to be growing, and they have Bull, but they have to deal with 28 different countries, and a weak investment community.

- China has had major funding support, has installed many very large systems, and is developing its own core technologies, but has a smaller user base, many different custom systems and currently is experiencing low utilization of its largest computers.

## TABLE OF CONTENTS

|                                                                                    | Ρ. |

|------------------------------------------------------------------------------------|----|

| Executive Summary                                                                  | 3  |

| Many Different Architectures Are Being Researched                                  | 3  |

| GPU and Accelerators Will be in a Number of Special Purpose Systems                | 3  |

| Power Consumption is a Major Concern                                               | 3  |

| Most Aren't Focused on Only Peak Performance                                       | 4  |

| A Wide Mix in Budgets for Developing and Building These Exascale Systems           | 4  |

| Ease-of-use Will Require Major Investments                                         | 4  |

| Exciting New Hardware Trends                                                       | 4  |

| Interesting New Software Trends                                                    | 4  |

| Partnerships for Developing These Systems                                          | 5  |

| Many National Programs Have Developed to Support These Efforts                     | 5  |

| Strengths and Weaknesses in Exascale Plans and Capabilities of Different Countries | 6  |

| IN THIS STUDY                                                                      | 1  |

| Methodology                                                                        | 1  |

| Project Goals and Objectives                                                       | 1  |

| Research Specifications:                                                           | 1  |

| Ease of Use Metrics                                                                | 2  |

| Definitions                                                                        | 4  |

| The Leadership Computers Facilities Researched in the Study                        | 4  |

| HPC at the French Alternative Energies and Atomic Energy Commission(CEA)           | 10 |

| The Parameters Tracked for Each Leadership System                                  | 11 |

| STUDY RESULTS: PRIMARY COMPARISONS                                                 | 13 |

| Comparisons of System Attributes                                                   | 13 |

| System Attributes: Planned Performance                                             | 13 |

| System Attributes: Architecture and Node Design                                    | 14 |

| System Attributes: Power                                                           | 16 |

| System Attributes: MTBF Rates                                                      | 17 |

| System Attributes: KPIs                                                            | 19 |

| Comparisons of Prices                                                              | 21 |

| Comparison of System Prices                                                        | 21 |

| Comparison of System Prices: Who's Paying for It?                                  | 23 |

| Comparisons of Ease-Of-Use                                                         | 24 |

| Ease-of-Use: Planned New Features                                                  | 24 |

| Ease-of-Use: Porting/Running of New Codes on a New Computer                        | 26 |

| Ease-of-Use: Missing Items that Reduce Ease-of-Use                                 | 30 |

## TABLE OF CONTENTS – Continued

|                                                                                         | Ρ. |

|-----------------------------------------------------------------------------------------|----|

| Ease-of-Use: Overall Ability to Run Leadership Class Problems                           | 31 |

| Comparisons of Hardware Attributes                                                      | 33 |

| Hardware Attributes: Processors                                                         | 33 |

| Hardware Attributes: Memory Systems                                                     | 35 |

| Hardware Attributes: Interconnects                                                      | 37 |

| Hardware Attributes: Storage                                                            | 38 |

| Hardware Attributes: Cooling                                                            | 40 |

| Hardware Attributes: Special Hardware                                                   | 41 |

| Hardware Attributes: Estimated Utilization                                              | 43 |

| Comparisons of Software Attributes                                                      | 44 |

| Software Attributes: OS and Special Software                                            | 44 |

| Software Attributes: File Systems                                                       | 46 |

| Software Attributes: Compilers and Middleware                                           | 47 |

| Software Attributes: Other Software                                                     | 49 |

| Comparisons of Supporting Research & Development                                        | 51 |

| R&D Plans                                                                               | 51 |

| R&D Plans: Partnerships                                                                 | 53 |

| Additional Observations                                                                 | 55 |

| KEY SUPPORTING QUESTIONS RESEARCHED                                                     | 57 |

| How important is access to this type of computer to your research/science?              | 57 |

| How important is it to your research to have a first class world leading supercomputer? | 57 |

| How important is it to your NATION to have a world leading supercomputer?               | 57 |

| What would happen if you had to only use a scale out vanilla cluster or a cloud?        | 57 |

| IDC Assessment of Different Countries Exascale Capabilities                             | 58 |

| Exascale Capabilities for the USA                                                       | 58 |

| Exascale Capabilities for Europe                                                        | 58 |

| Exascale Capabilities for China                                                         | 59 |

| FUTURE OUTLOOK                                                                          | 61 |

| There Will Be a Broad Range of New Technologies                                         | 61 |

| Strong National Leadership-Class Supercomputer Facilities Play An Important Role        | 61 |

| DISCLAIMER AND COPYRIGHT                                                                | 62 |

## LIST OF TABLES

|                                                                        | Ρ. |

|------------------------------------------------------------------------|----|

| Table 1 The Supercomputers Evaluated in This Study                     | 10 |

| Table 2 System Attributes: Planned Performance                         | 13 |

| Table 3 System Attributes: Architecture and Node Design                | 15 |

| Table 4 System Attributes: Power                                       | 17 |

| Table 5 System Attributes: MTBF Rates                                  | 18 |

| Table 6 System Attributes: KPIs                                        | 19 |

| Table 7 Comparison of System Prices                                    | 21 |

| Table 8 Comparison of System Prices: Who's Paying for It?              | 24 |

| Table 9 Ease-of-Use: Planned New Features                              | 26 |

| Table 10 Ease-of-Use: Porting/Running of New Codes on a New Computer   | 28 |

| Table 11 Ease-of-Use: Missing Items that Reduce Ease-of-Use            | 30 |

| Table 12 Ease-of-Use: Overall Ability to Run Leadership Class Problems | 32 |

| Table 13 Hardware Attributes: Processors                               | 34 |

| Table 14 Hardware Attributes: Memory Systems                           | 36 |

| Table 15 Hardware Attributes: Interconnects                            | 37 |

| Table 16 Hardware Attributes: Storage                                  | 39 |

| Table 17 Hardware Attributes: Cooling                                  | 40 |

| Table 18 Hardware Attributes: Special Hardware                         | 42 |

| Table 19 Hardware Attributes: Estimated System Utilization             | 43 |

| Table 20 Software Attributes: OS and Special Software                  | 45 |

| Table 21 Software Attributes: File Systems                             | 46 |

| Table 22 Software Attributes: Compilers and Middleware                 | 48 |

| Table 23 Software Attributes: Other Software                           | 50 |

| Table 24 R&D Plans                                                     | 52 |

| Table 25 R&D Plans: Partnerships                                       | 54 |

| Table 27 Additional Comments & Observations                            | 55 |

| Table 28 IDC Assessment of the Major Exascale Providers: USA           | 58 |

| Table 29 IDC Assessment of the Major Exascale Providers: Europe/EMEA   | 58 |

| Table 30 Assessment of Exascale Providers: China                       | 59 |

#### **IN THIS STUDY**

### Methodology

## Project Goals and Objectives

This IDC report summarizes a number of leadership-class supercomputer developments on-going and planned within the next five years at leading supercomputer sites around the world. In essence, it is an attempt to capture in significant detail, supported by technical information, some of the most important -- and technologically forward learning -- developments in supercomputers from today out to 2020 and beyond. This particular time frame coincides with when Japan's Riken's Post-K system is scheduled to begin operations.

As such, the report looks at supercomputer development plans for most of the major supercomputer developer and user nations, but it is heavily focused on those in the United States, China and Europe, encompassing a wide range of developers richly experienced in leading-edge supercomputer development as well those that are relatively new entrants to the field.

- The analysis captures many of the most salient technical R&D elements of the new systems that are planned for the next few years, and also considers the related commitment of financial and other resources committed the efforts.

- In addition, it attempts to compare and contrast the various national efforts on the bias of their technological validity and their potential for driving significant gains in furthering the state of the art in supercomputer development

- All work on this effort is to be completed before December 27, 2016.

#### Research Specifications:

For this study, IDC analysts collected a wide range of technical and other data relating to the planned development efforts of major HPC projects around the world, with a time frame that spanned developments currently underway and those with completion dates targeted out to 2020. The information and analysis on these projects collected from various foreign countries were based on a list reviewed approved by RIKEN. Key collection metrics included

- Specifications (type of the processor, peak performance, etc.) of the next-generation computers in research and development in other countries.

- Information specifics on the investments in the research and development of the nextgeneration computers already in progress in other countries.

IDC analysts used that data to glean key insights and projections on the significant development trends of the next generation of leadership-class supercomputers across a wide range of countries and individual development projects.

- IDC analysis was performed on the basis of the information collected through interviews and through the IDC information collection process.

- Discussions and analysis were conducted based on the reliability of the information collected.

IDC indicated whether the information was solid, sound, speculative, or modeled.

IDC exploited its strong relationships with international HPC users, vendors, and funders around the world to present a detailed, balanced view of these areas, including an analysis of strengths and weaknesses in each area.

IDC analysis also describes the very real dangers these initiatives create for Japanese science if Japan does not fund a successor to the K supercomputer, as well as the benefits for science of the architectural approach RIKEN has been taking - especially the suitability of the RIKEN approach for grand challenge science and support for Nobel laureate-class work. IDC believes that the RIKEN approach has some important advantages over the approaches being taken in the U.S., China and Europe.

- IDC examines the uses and limitations of other approaches, such as typical cluster architectures with GPUs or other accelerators.

- Key related workforce issues were also examined as IDC studies have confirmed that there is a worldwide shortage of qualified candidates for important HPC job categories, especially algorithm developers, parallel programmers, system administrators, and candidates with expertise spanning computational science and a scientific domain.

In addition to the exploration of technical attributes, IDC surveyed a number of leadership-class supercomputer users to gain insights on the importance of those systems to their overall research efforts as well as to gather theory insights on how the lack of such a system could affect their ability to conduct leading-edge research going forward.

- How important is access to this type of computer to your research/science?

- How important is it to your work/research to have a first class world leading supercomputer?

- How important is it to your NATION to have a first class world leading supercomputer?

- What would happen to your work if you had to only use a scale out vanilla cluster or a cloud?

#### Ease of Use Metrics

In order to accurately assess the overall complexity required to either upgrade or implement a completely new leadership class supercomputer, IDC analysists used the following methodology and associated ease of use metrics to help define, quantify, and ultimately compare the overall ease of use across the range of systems examined.

It is important to note that many of the decisions for assigning ease of use ratings were heavily influenced by the presence or absence of key architectural features that comprise each of the systems described in this report.

- Systems that were considered to be have more ease of use issues included those with heterogeneous architectures, mixed CPU/GPU configurations, or new or untested processors. Additionally, new or innovative memory or storage schemes, such as burst buffers or related SSD technology, could negatively affect the overall ease of use for a particular system.

- In contrast, systems that were essentially upgrades to existing systems, especially those

purchased from commercial vendors, and based largely on COTS hardware and open source

software, were considered to have fewer ease of use concerns, and they generally received

higher ease of use ratings.

#### Scale and Definitions

IDC assessed the overall ease of use of each leadership-class supercomputer for porting and/or running of new or existing codes on a new computer. That assessment was divided into three distinct elements:

Initial writing/porting of new codes on new computer

- Performance tuning of new and existing codes for optimized results.

- Ease-of-use for existing running codes (porting/certification).

- Ease-of-use for existing running codes (optimization, redesign, rewriting)

Specific factors for consideration within each category were:

#### *Initial writing/porting of new codes on new computer*

- Composition of overall system architecture

- Composition of processor base(s), node size, node count etc.

- Inclusion of accelerators

- Characteristics of cache and/or memory: size, composition (DDR4, NVRAM, etc.), access times, memory bandwidth, memory configuration per chip, node, or system

- Complexity of memory hierarchy, interconnect scheme, or file system,

- OS and related software stack composition and complexity

- Linkages to legacy code

- Availability/sophistication of code development/optimization tools

- Availability of skilled programmers either in-house or for hire

#### *Ease-of-use for existing running codes (porting/certification)*

- Changes in overall system architecture from existing system

- Changes in processor base(s), node size, node count etc.

- Inclusion or change in accelerator use

- Changes in memory size, speed, configuration per chip, node, or system from predecessor system

- Impact of new, existing, or different memory hierarchy, interconnect scheme, or file system

- Changes in OS and related software stack composition and complexity

- Issues with legacy code composition including age, type, language, size and complexity

- Availability/sophistication of code porting tools

- Existing code base composition: open source, in-house, or ISV

- Availability of skilled programmers for legacy and/or new code base

- Complexity of certification and/or verification and validation process

- Data integrity issues

- Data storage formats

#### Ease-of-use for existing running codes (optimization, redesign, rewriting).

- Complexity, composition, or uniqueness of system architecture, processors composition, memory architecture, interconnect scheme and file system

- Availability and sophistication of scheduling, resource management, job queuing management and related run-time operation software

- Availability/sophistication of code development/optimization tools

- Availability/functionality of hardware/software monitors and operational data collection tools

#### Ease of Use Rating Scheme

For each of these measures, IDC analysts used the following numerical rating scale to assess the effort needed to implement a various ease of use features for each leadership-class supercomputers.

- The scale goes from 1 to five, with five being defined as a simple process with only some ease of use requirements, and 1 being a highly complex process with many difficult ease of use requirements.

- In addition, IDC analysts used a score of -1 for situations where the process may consist of considerable, if not insurmountable, ease of use requirements.

#### The complete scale is as follows:

- 5 = MOVING TO THE NEW SYSTEM IS A SIMPLE PROCESS WITH LITTLE OR NO NEW EASE OF USE REQUIREMENTS

- 4 = MOVING TO THE NEW SYSTEM IS A SIMPLE PROCESS WITH SOME EASE OF USE REQUIREMENTS IN THE PROJECT

- 3 = MOVING TO THE NEW SYSTEM WILL REQUIRE AN AVERAGE LEVEL OF NEW EASE OF USE CAPABILITIES TO MAKE THE SYSTEM WORK FOR A BROAD SET OF USERS

- 2 = MOVING TO THE NEW SYSTEM IS A COMPLEX PROCESS WITH MANY EASE OF USE REQUIREMENTS TO MAKE THE SYSTEM WORK FOR A BROAD SET OF USERS

- 1 = MOVING TO THE NEW SYSTEM IS A VERY COMPLEX PROCESS WITH MANY DIFFICULT EASE OF USE REQUIREMENTS TO MAKE THE SYSTEM WORK FOR A BROAD SET OF USERS

- -1 = MOVING TO THE NEW SYSTEM IS A HIGHLY COMPLEX PROCESS WITH CONSIDERABLE, PERHAPS INSURMOUNTABLE EASE OF USE REQUIREMENTS

It should be noted that not all of the considerations listed above applied to every system examined, and instead the rating given to each system was based on a determination of the key ease of use features that would have the greatest impact on the overall ease of use of any given system. examined.

Finally, it should be noted that this scale inherently assumes that programming any new system is difficult. As such even for those machines that are highly rated -say with a four or five - programming is still considered to be a complex task, but from a comparative perspective, it will likely be easier to program than those with a lower ease of use score, say one or two.

#### Definitions

#### The Leadership Computers Facilities Researched in the Study

The following is a short summary of the various exascale systems and their associated competing facility examined in this study. This section is not meant to be a rigorous examination that compares and contrasts the various facilities that will house these HPCs, but instead it is a quick compendium that highlights significant features or value-added distinctions unique to each site.

#### The Sierra HPC at the US Department's Lawrence Livermore National Laboratory (LLNL)

Located in Livermore, California, U.S., LLNL's defining responsibility is ensuring the safety, security and reliability of the nation's nuclear deterrent. Yet LLNL's mission is broader than stockpile stewardship, as dangers ranging from nuclear proliferation and terrorism to energy shortages and

climate change threaten national security and global stability. The Laboratory's science and engineering are being applied to achieve breakthroughs for counterterrorism and nonproliferation, defense and intelligence, energy and environmental security. The lab employ 2,700 scientists and engineers (more than 40% of whom are Ph.Ds.). The computing and simulation infrastructure at LLNL spans multiple buildings with large computer rooms. The largest facility was designed specifically to house the landmark Purple and Blue Gene/L systems and their successors, which currently include Sequoia, Vulcan, and Zin, among others. This computer facility provides 48,000 ft<sup>2</sup> and 30 MW of power for systems and peripherals, and additional power for the associated machine-cooling system.

# The Summit HPC at the US Department of Energy's Oak Ridge National Laboratory (ORNL)

Located in eastern Tennessee, near Knoxville in the U.S., ORNL is the largest Department of Energy science and energy laboratory, conducting basic and applied research to deliver transformative solutions to compelling problems in energy and security. ORNL's diverse capabilities span a broad range of scientific and engineering disciplines, enabling the Laboratory to explore fundamental science challenges and to carry out the research needed to accelerate the delivery of solutions to the marketplace. The lab has a staff of more than 4,600, including scientists and engineers in more than 100 disciplines. ORNL's supercomputing program has grown from humble beginnings to deliver some of the most powerful systems in the world. On the way, it has helped researchers deliver practical breakthroughs and new scientific knowledge in climate, materials, nuclear science, and a wide range of other disciplines.

#### The Aurora HPC at the US Department of Energy's Argonne National Laboratory (ANL)

Located outside Chicago, Illinois, U.S., ANL is a multidisciplinary science and engineering research center, where scientists and engineers work together to answer some of the biggest questions facing humanity, from how to obtain affordable clean energy to protecting ourselves and our environment. The laboratory works in concert with universities, industry, and other national laboratories on questions and experiments too large for any one institution to do by itself. Through collaborations domestically and around the world, ANL strives to discover new ways to develop energy innovations through science, create novel materials molecule-by-molecule, and gain a deeper understanding of the earth, is climate, and the cosmos. ARL is staffed by over 3,200 employees, almost half of them scientists and engineers. and there are over 7,000 facility users. The Argonne Leadership Computing Facility's (ALCF) mission is to accelerate major scientific discoveries and engineering breakthroughs for humanity by designing and providing world-leading computing facilities in partnership with the computational science community.

# The CORI HPC at the U.S. Department of Energy's National Energy Research Scientific Computing Center

As one of the largest facilities in the world devoted to providing computational resources and expertise for basic scientific research, NERSC is a world leader in accelerating scientific discovery through computation. NERSC is a division of the Lawrence Berkeley National Laboratory, located in Berkeley, California, U.S. More than 5,000 scientists use NERSC to perform basic scientific research across a wide range of disciplines, including climate modeling, research into new materials, simulations of the early universe, analysis of data from high energy physics experiments, investigations of protein structure, and a host of other scientific endeavors. NERSC provides some of the largest computing and storage systems available anywhere, but what distinguishes the center is its success in creating an environment that makes these resources effective for scientific research. NERSC systems are

reliable and secure, and provide a state-of-the-art scientific development environment with the tools needed by the diverse community of NERSC users.

# The NERSC-9 HPC at U.S. Department of Energy's Lawrence Berkeley National Laboratory

Located in Berkeley, California, U.S., in the world of science, Lawrence Berkeley National Laboratory is synonymous with "excellence." Thirteen Nobel prizes are associated with Berkeley Lab. Seventy Lab scientists are members of the National Academy of Sciences (NAS), one of the highest honors for a scientist in the United States. Berkeley Lab fosters groundbreaking fundamental science that enables transformational solutions for energy and environment challenges, using interdisciplinary teams and by creating advanced new tools for scientific discovery, and the lab employs approximately 3,232 scientists, engineers and support staff. The LBNL computing center is operated by the NERSC center outlined above.

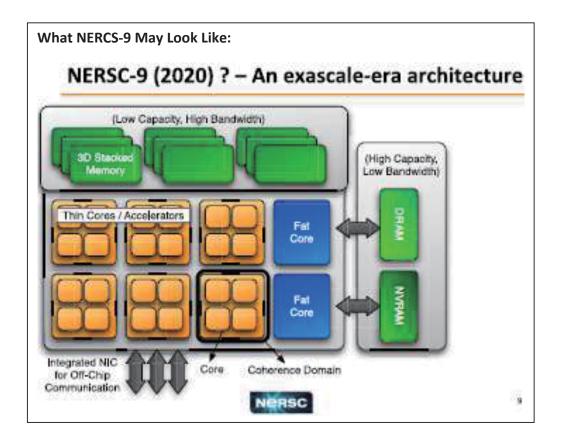

The two diagrams bellow are from Nicholas J. Wright; NERSC-9 Chief Architect, NUG meeting, March 24, LBNL:

## A Site Example: NERSC's Ten-Year Plans

#### Timeline:

- 2016 NERSC-8, CORI operational

- 2018 25MW site power upgraded

- 2020 NERSC-9 operational -- 150 to 300 Petaflops

- 2021 35MW site power upgraded

- 2024 NERSC-10 -- Exascale capable system is operational

- 2028 NERSC-11 -- 5 to 10 Exaflops is operational

#### Project Goals:

- Provide a significant increase in computational capabilities over the Edison system, at least 16x on a set of representative DOE benchmarks

- Platform needs to meet the needs of extreme computing and data users by <u>accelerating workflow performance</u>

- Platform should provide a vehicle for the demonstration and development of exascale-era technologies

- NERSC will partner with vendors on Non-Recurring Engineering (NRE) projects to maximize the usability and performance of the machine

- Additional NERSC-9 Requirements:

- Non-volatile (page addressable memory) = 10's of PBs, 10's TB/sec

- Spinning disk = 50 PBs, 1 TB/sec

- Tape = 100's PBs, 10's GB/sec

- Burst buffer > 90 PBs, >5 TB/sec

- To develop these requirements, they held many face-to-face meetings with all vendors and all of their major user groups - a requirements workshop with each location/group -- <u>http://www.nersc.gov/science/hpc-requirements-reviews/exascale/</u>

Application Mix Used for Setting the NERSC-9 Requirements:

| MiniApp                          | Description                                                          | Language      |

|----------------------------------|----------------------------------------------------------------------|---------------|

| miniDFT<br>(Quantum<br>Espresso) | Plain-wave Density Functional Theory (DFT)                           | Fortran       |

| MILC                             | Lattice Quantum Chromodynamics (QCD). Sparse<br>matrix inversion, CG | c             |

| GTC-P                            | Particle-in-cell magnetic fusion                                     | c             |

| UMT                              | Unstructured-Mesh deterministic radiation<br>Transport               | C/C++/Fortran |

| SNAP                             | Neutron particle transport application                               | Fortran       |

| PENNANT                          | Unstructured finite element                                          | ¢             |

| Meraculous                       | De novo genome assembly                                              | UPC           |

| MiniPIC                          | Particle in cell for accelerators                                    | C++           |

| HPCG                             | High Performance Conjugate Gradient                                  | C             |

# The Cheyenne HPC at the U.S. National Science Foundation's National Center for Atmospheric Research

Located in Boulder Colorado, U.S., NCAR is a federally funded research and development center devoted to service, research and education in the atmospheric and related sciences. NCAR's mission is to understand the behavior of the atmosphere and related Earth and geospace systems and specifically; to support, enhance, and extend the capabilities of the university community and the broader scientific community, nationally and internationally; to foster the transfer of knowledge and technology for the betterment of life on Earth. The National Science Foundation is NCAR's sponsor, with significant additional support provided by other U.S. government agencies, other national governments and the private sector. The Cheyenne HPC will be installed at the NCAR-Wyoming Supercomputing Center, a 150,000 square foot facility that provides advanced computing services to scientists across the nation who study weather, oceanography, air pollution, climate, space weather, energy production, seismology, carbon sequestration, computational science, and other topics related to the Earth system.

# The TaihuLight HPC built by Sunway and installed at China's National Supercomputer Center in Jiangsu, China.

The system, designed by the Beijing-funded National Research Center of Parallel Computer Engineering and Technology (NRCPC), is located at the National Supercomputing Center in the city of Wuxi, in Jiangsu province, China. The Chinese Super Computing Center (Wuxi) was established after a joint investment in 2006 by the Ministry of Science and Technology and the Wuxi Government and is one of the most advanced high-performance computing platforms in the China. Wuxi, Tsinghua University and Jiangsu Industrial Technology Research Institute also signed a cooperative agreement entrusting the National Supercomputing Wuxi Center to Tsinghua University to manage and operate the facility, which is aimed at actively carrying out software development, focusing on propelling Chinese supercomputing application capability.

Note: IDC has also included information on the Sunway version that is in competition for the China 2020 exascale program. China will be holding a contest in 2018 to decide which designs will receive funding to be built at the exascale level. Both the Sunway and NUDT designs have a good chance in this competition. The design point is 1 EF peak, .6 EF on the Linpack test, and under 35 MW power consumption.

#### The TianHe2 A (and 3) at China's National University of Defense Technology

The National University of Defense Technology (NUDT) is a top military academy, as well as a research national key university located in Changsha, Hunan Province, China. It is under the direct leadership of China's Central Military Commission, and dual management of the Ministry of National Defense of the People's Republic of China and Ministry of Education. It is a designated center for Beijing-funded programs, Project 211 and Project 985, the two national plans for facilitating the development of Chinese higher education. NUDT now has over 2,000 faculty members of which nearly 300 are professors. There are 15,700 full-time students including 8,900 undergraduates and 6,800 graduates. NUDT has a long history of HPC development, developing one of China's first HPCs, the Yinhe-1 in 1983, which had a theoretical peak performance of one gigaflop/s.

Note: IDC has also included information on the possible NUDT system version that is in competition for the China 2020 exascale program. China will be holding a contest in 2018 to decide which designs will receive funding to be built at the exascale level. Both the Sunway and NUDT designs have a good

chance in this competition. The design point is 1 EF peak, .6 EF on the Linpack test, and under 35 MW power consumption.

#### The Hazel Hen at the High Performance Computing Center Stuttgart, Germany (HLRS)

HLRS was established in 1996 as the first national German High Performance Computing center. It is a research and service institution affiliated with the University of Stuttgart, offering services to academic users and industry. HLRS focuses on the operation of leading edge HPC systems, teaching and training for HPC programming and simulation, research in the field of HPC together with national and international partners, collaboration with industry in R&D, and providing access to HPC systems through hww - a public private partnership with commercial partners T-Systems and Porsche. HLRS has been open to European users since 2010 through the EU-wide PRACE program.

# The SuperMUC at Leibniz Supercomputer Centre (LRZ) of the Bavarian Academy of Science and Humanities,

LRZ provides services to the scientific and academic communities that include general IT services for more than 100,000 university customers in Munich and for the Bavarian Academy of Sciences and Humanities (BAdW), a communications infrastructure called the Munich Scientific Network (Münchner Wissenschaftsnetz, MWN), archiving and backup of large amounts of data on extensive disk and automated magnetic tape storage, and a technical and scientific high performance Supercomputing Centre for all German universities. The LRZ offers computing power on several different levels including the national supercomputing system SuperMUC, two more supercomputers (a SGI UV with 2,080 cores, and a MEGWARE Cluster with 1,424 cores) which can be accessed by researchers from all Bavarian universities, and an Intel IA32/EM64T-based Linux cluster which can be accessed by researchers from the Munich universities. These machines serve as platforms for running a diverse spectrum of applications, as well as developing and testing serial and parallel programs.

#### The Piz Daint at the Swiss National Supercomputer Center (CSCS) in Lugano Switzerland

Founded in 1991, CSCS, the Swiss National Supercomputing Centre, develops and provides the key supercomputing capabilities required to solve important problems to science and/or society. The centre enables world-class research with a scientific user lab that is available to domestic and international researchers through a transparent, peer-reviewed allocation process. CSCS's resources are open to academia and are available as well to users from industry and the business sector. The centre operates dedicated computing facilities for specific research projects and national mandates, e.g. weather forecasting. It is the national competence centre for high-performance computing and serves as a technology platform for Swiss research in computational science.

#### The D-Wave System at the NASA Ames Research Center on Moffett Field, California, US

NASA Ames Research Center, one of ten NASA field centers, is located in the heart of California's Silicon Valley. For more than 76 years, Ames has led NASA in conducting world-class research and development in aeronautics, exploration technology and science aligned with the center's core capabilities. Ames' key goals include maintaining expertise in information technology, aerospace and aeronautics research and engineering, conduct research in space, Earth, lunar and biological sciences, developing lead status for NASA in small spacecraft missions, expanding public and private partnerships, and contributing innovative, high performance and reliable exploration technologies. NASA's Quantum Artificial Intelligence Laboratory (QuAIL), which operates the D-Wave system, is the space agency's hub for experiments to assess the potential of quantum computers to perform calculations that are difficult or impossible using conventional supercomputers.

#### UK Three System Upgrade at the University of Edinburgh, ECMWF, Daresbury Lab.

The Science and Technology Facilities Council (STFC), the UK government sponsored research organization that works with both national industrial and research partners on systems and software projects and that funds the Daresbury Lab, is underwriting a \$412 million investment to support a grand OpenPower undertaking that will bring three new systems into play at three of the UK's leading HPC development centers.

## HPC at the French Alternative Energies and Atomic Energy Commission(CEA)

The French Alternative Energies and Atomic Energy Commission (CEA) is a key player in research, development and innovation in four main areas: defense and security, nuclear energy (fission and fusion), technological research for industry, fundamental research in the physical sciences and life sciences. The CEA is established in ten centers spread throughout France, and it works in partnership with many other research bodies, local authorities and universities. Within this context, the CEA is a stakeholder in a series of national alliances set up to coordinate French research in energy (ANCRE), life sciences and health (AVIESAN), digital science and technology (ALLISTENE), environmental sciences (AllEnvi) and human and social sciences (ATHENA). CEA has 15 958 technicians, engineers, researchers and staff, spread across 51 joint research units, has created 187 start-ups since 1972 in the innovative technologies sector, and currently has 438 ongoing European research projects. The scientific computing complex at the CEA facility in Bruyères-le-Châtel (DAM/Île de France) hosts one of Europe's largest high-performance computing facilities, used for defense, industrial and research applications. It houses the large infrastructure operated by CEA DAM specifically for defense-related programmers, featuring the Atos/Bull Tera1000-1 supercomputer (with a processing power of 2.5 petaflops), which will be joined in 2017 by the 25-petaflop Tera1000-2.

#### Table 1

| -                 | -             |                                      | -            |         |                          |

|-------------------|---------------|--------------------------------------|--------------|---------|--------------------------|

| Computer<br>Names | Project Names | Prime Developer/<br>Industry Partner | Organization | Country | Planned Delivery<br>Year |

| Sierra            | CORAL         | IBM, NVIDIA,<br>Mellanox             | LLNL         | USA     | 2017, 3Q                 |

| Summit            | CORAL         | IBM                                  | ORNL         | USA     | 2017, 3Q                 |

| Aurora            | CORAL         | Intel/Cray                           | ANL          | USA     | 2018, 4Q                 |

| CORI              | NERSC-8       | Cray                                 | LLBL         | USA     | 2016, 4Q                 |

| Crossroads        | APEX 2020     | TBD                                  | LANL         | USA     | 2020, 4Q                 |

| NERSC-9           | APEX 2020     | TBD                                  | LLBL         | USA     | 2020, 4Q                 |

| Cheyenne          | U/U/C*        | SGI                                  | NCAR         | USA     | 2017, 3Q                 |

| TaihuLight        | Sunway        | NRCPC                                | Sunway       | China   | 2016<br>(2020, 4Q)       |

#### The Supercomputers Evaluated in This Study

| Computer<br>Names                          | Project Names             | Prime Developer/<br>Industry Partner | Organization                                           | Country     | Planned Delivery<br>Year    |

|--------------------------------------------|---------------------------|--------------------------------------|--------------------------------------------------------|-------------|-----------------------------|

| (And the<br>Sunway 2020<br>System)         |                           |                                      |                                                        |             |                             |

| TianHe2 A<br>(And the NUDT<br>2020 System) | Milky Way 3               | NUDT/Inspur                          | NUDT                                                   | China       | 2017 2Q or 3Q<br>(2020, 4Q) |

| Hazel Hen                                  | U/U/C                     | Cray                                 | HLRS                                                   | Germany     | 2015                        |

| SuperMUC                                   | Phase 2                   | Lenovo/IBM                           | LRZ                                                    | Germany     | 2015                        |

| Piz Diant                                  | U/U/C                     | Cray                                 | CSCS                                                   | Switzerland | 2016                        |

| D-Wave                                     | U/U/C                     | U/U/C                                | Google/NASA                                            | USA         | 2015                        |

| UK Three<br>System Upgrade                 | S&T Facilities<br>Council | IBM, others                          | University of<br>Edinburgh,<br>ECMWF,<br>Daresbury Lab | UK          | 2018, 3Q                    |

| CEA/Bull                                   | Tera 100<br>Follow-on     | Bull                                 | CEA/ Bull                                              | France      | 2020, 3Q                    |

### The Supercomputers Evaluated in This Study

Source: IDC 2016

\* U/U/C = Uncertain/Unknown/Confidential

## The Parameters Tracked for Each Leadership System

For the purpose of this study, and in considered consultation with RIKEN, IDC used the following technical parameters in tracking the major leadership-class supercomputers around the world.

Systems Attributes: consisted of overall planned system attributes that included:

- Planned performance—the theoretical perk performance of the system, typically measured in petaflops,

- Architecture and node design—the overall architectural configuration of the system such as node composition, memory and interconnect scheme, and file system.

- Power--the maximum power use by the system, typically measured in megawatts

- MTBF- the mean time between failures envisioned for the system that include hardware and software related failures.

KPI-key performance indicators that measure how well the system performs compared with some independent, but representative performance parameter, such as a multiple of performance improvement over an existing or companion system.

**Prices;** consisted of overall system prices - including overall procurement costs, breakdowns on hardware and software maintenance costs, additional NRE considerations, as well as listings of the particular funding organization.

**Ease of Use**–defined as the ability for programmers to use the full computational capabilities of the system, which in the study consisted of four different ease of use categories.

- Planned New Features

- Porting/Running of New Codes on a New Computer

- Missing Items that Reduce Ease-of-Use

- Overall Ability to Run Leadership Class Problems

**Hardware Attributes** - consisted of the collection of key hardware specifications comprising the leadership-class supercomputer. Key metrics included:

- Processors

- Memory Systems

- Interconnects1

- Storage

- Cooling

- Special Hardware

- Estimated Utilization

**Software Attributes** - consisted of the collection of key software specifications/features comprising the leadership-class supercomputer. Key metrics included:

- OS and Special Software

- File Systems

- Compilers and Middleware

- Other Software

### STUDY RESULTS: PRIMARY COMPARISONS

## **Comparisons of System Attributes**

#### *System Attributes: Planned Performance*

As seen in Table 2, there are a number of major leadership-class HPCs in the planning and development stage targeted for deployment between 2016 and 2020. In addition to Japan, such development is being considered across a wide range of major HPC suppliers and user regions including China, the EU, and the United States.

- Most of these systems can be considered pre-exascale designs: systems that will underwrite much of the technology critical to the development of the hardware and software necessary to support the spate of exascale systems planned for the 2020 to 2022-time frame.

- As such, the bulk of the system planned for the next four years target a peak performance capability generally between 10 and 300 teraflops, with the bulk of the lower-end systems closer to completion this year or the next, while higher performance systems are targeted for completion closer to 2020.

Notes about the power goals in table 2 below:

- 1. Some of the GF/W rating for these systems are a measure of the theoretical peak performance the system in PFLOPS divided by their total power consumption in MWs.

- This is the case for systems like the Sierra, Summit, Aurora, SuperMUC, Hazel Hen and Piz Daint. In these cases, either the site specifically listed that number as their GF/W metric or IDC did the calculation using stated/estimated peak performance and power numbers.

- 2. Other sites used different metrics:

- The Cori system has a calculated peak GF/W of 8.1, but the site specifications cited 14-16 GF/W, which is the performance rating of the Knight Landing processor they will use in the system.

- The Crossroads and NERSC-9 systems specifically called out 35 GF/W for peak performance, and 10-12 GF/W for Linpack performance.

- The Cheyenne HPC at has a 3.06 GF/W based on system peak performance and total system power use. But they also indicated that they were targeting 34 MF/W based on sustained performance on NCAR workloads.

- The TaihuLight metric of 6 GF/W was based on Linpack performance, as was the case with the TianHe2 A system.

- 3. The CEA/Bull system was simply listed as overall system goal.

#### Table 2

## System Attributes: Planned Performance

| Computer<br>Names | Planned Delivery<br>Date | Planned Performance PF | GF/Watt Goals |

|-------------------|--------------------------|------------------------|---------------|

| Sierra            | 2017, 3Q                 | 120-150                | 11.5 to 13.2  |

## System Attributes: Planned Performance

| Computer<br>Names           | Planned Delivery<br>Date    | Planned Performance PF                                       | GF/Watt Goals                              |

|-----------------------------|-----------------------------|--------------------------------------------------------------|--------------------------------------------|

| Summit                      | 2017, 3Q                    | 150-300                                                      | 11.5 to 13.2                               |

| Aurora                      | 2018, 4Q                    | >180                                                         | 13.0                                       |

| CORI                        | 2016, 4Q                    | >30                                                          | 14 to 16                                   |

| Crossroads                  | 2020, 4Q                    | 150-300                                                      | 35+ (peak goal)<br>10-12 likely on Linpack |

| NERSC-9                     | 2020, 4Q                    | 150-300                                                      | 35+ (peak goal)<br>10-12 likely on Linpack |

| Cheyenne                    | 2017, 3Q                    | 5.34                                                         | 3.0                                        |

| TaihuLight<br>(Sunway 2020) | 2016<br>(2020, 4Q)          | 125 peak/93 LP<br>(1,000)                                    | 6<br>(Around 30)                           |

| TianHe2 A<br>(NUDT 2020)    | 2017 2Q or 3Q<br>(2020, 4Q) | Could be as high as 200-300 or at<br>least 100+LP<br>(1,000) | 4-5<br>(20-30)                             |

| Hazel Hen                   | 2015                        | 7.42                                                         | 2.3                                        |

| SuperMUC                    | 2015                        | 3.58                                                         | 3.2                                        |

| Piz Daint                   | 2016                        | 15                                                           | 6.45                                       |

| D-Wave                      | 2015                        | NA as it doesn't do FLOPS                                    | NA as it doesn't do FLOPS                  |

| UK Three<br>System Upgrade  | 2018, 3Q                    | U/U/C                                                        | U/U/C                                      |

| CEA/Bull                    | 2020, 3Q                    | 1,000                                                        | 35 to 50                                   |

Source: IDC 2016

U/U/C = Uncertain/Unknown/Confidential

## System Attributes: Architecture and Node Design

As seen in table 3, there are a wide range of different architectural design paths to a pre-exascale system. During this study, two major design options emerged.

- Some are looking to partner with a commercial vendor, such as Cray or IBM, to help them develop a leadership-class system that is in keeping with the overall product offerings of their commercial partner, such as the Cheyenne SGI system at NCAR.

- Others, such as NUDT's Tianhe-2 A group in China, are essentially looking to custom-build systems that likely will be produced in very limited quantiles, primarily for in-house use with some but perhaps even no commercial counterpart.

In addition, it is clear that there is no agreed upon architectural scheme for these pre-exascale systems. Variants noted here include designs with various CPUs, including x86, POWER and ARM, others with hybrid CPU/GPU configurations, and a wide variety of new memory, node and interconnect schemes.

Finally, recent information on two additional 2020 exascale Chinese machines offer the following details:

- For a Sunway TaihuLight follow-on slated for 2022, the system will have a 20 teraflops/node capability with a total of 50,000 nodes, described as having a bootable accelerator architecture, yielding a peak performance of one exaflop.

- For an NUDT Tianhe-2A follow-on slated for 2020-2022, the system will have an 80 teraflops/node capability with a total of 12, 500 nodes described as a CPU + accelerator architecture, yielding a peak performance of one exaflop as well.

## Table 3

| Computer Names | Planned<br>Delivery Date | System<br>Architecture | Node Configuration                                           | Memory/Node                                                    |

|----------------|--------------------------|------------------------|--------------------------------------------------------------|----------------------------------------------------------------|

| Sierra         | 2017, 3Q                 | Custom                 | >1500 fat nodes, 40<br>TFLOPS/node                           | 512 GB DDR4 +HBM,<br>800 GB of NVRAM                           |

| Summit         | 2017, 3Q                 | Custom                 | >3400 fat nodes, 40<br>TFLOPS/node                           | 512 GB DDR4 +HBM,<br>800 GB of NVRAM                           |

| Aurora         | 2018, 4Q                 | Cray Shasta            | 50,000 nodes                                                 | Not yet decided                                                |

| CORI           | 2016, 4Q                 | Cray XC40              | 2 16-core Intel processors per node, KNL nodes 68 cores/node | 128GB (Phase I)                                                |

| Crossroads     | 2020, 4Q                 | Being designed         | Being designed                                               | Being designed                                                 |

| NERSC-9        | 2020, 4Q                 | Being designed         | Being designed                                               | Being designed                                                 |

| Cheyenne       | 2017, 3Q                 | SGI ICE XA cluster     | 4032 Nodes (dual socket nodes)                               | DDR4 64 GB/node on<br>3,168 nodes, 128<br>GB/node on 864 nodes |

#### System Attributes: Architecture and Node Design

| Computer Names              | Planned<br>Delivery Date    | System<br>Architecture           | Node Configuration                                                                             | Memory/Node                 |

|-----------------------------|-----------------------------|----------------------------------|------------------------------------------------------------------------------------------------|-----------------------------|

| TaihuLight<br>(Sunway 2020) | 2016<br>(2020, 4Q)          | Custom<br>(Custom)               | 40,960 nodes, each –one SW<br>chip/node<br>(Likely a large array of<br>accelerator like cores) | 32 GB                       |

| TianHe2 A<br>(NUDT 2020)    | 2017 2Q or 3Q<br>(2020, 4Q) | Custom<br>(Custom)               | FT-2000 ARM chip based<br>(Likely a CPU & accelerator mix)                                     | U/U/C                       |

| Hazel Hen                   | 2015                        | Cray XC40                        | 7712 nodes, 2 sockets/node                                                                     | 128 GB                      |

| SuperMUC                    | 2015                        | Lenovo NeXtScale<br>nx360 M5 WCT | 3072 nodes, 2 processors per node                                                              | 64 GB                       |

| Piz Diant                   | 2016                        | Cray XC30                        | 5272 nodes 1 cpu + gpu per<br>node,                                                            | 32 GB (DDR3)<br>6GB (GDDR5) |

| D-Wave                      | 2015                        | 2X Quantum<br>Computer           | 1000 qubits                                                                                    | NA                          |

| UK Three System<br>Upgrade  | 2018, 3Q                    | U/U/C                            | U/U/C                                                                                          | U/U/C                       |

| CEA/Bull                    | 2020, 3Q                    | Custom                           | U/U/C                                                                                          | U/U/C                       |

#### System Attributes: Architecture and Node Design

Source: IDC 2016

U/U/C = Uncertain/Unknown/Confidential

## System Attributes: Power

As seen in Table 4, concerns about power consumption and related efficiencies keeping total power needs for pre-exascale system generally below 30 MW, for even some of the most powerful machines. Such a trend may be a driving force towards the use of GPU and other accelerators, which can boost peak performance with a more forgiving energy requirement than a CPU-only configuration.

- In addition, many designers are looking for ways to better control the real-time power draw of their systems by using advanced techniques to power down portions of their systems not in use during a job or even a portion of a job.

- As such, many of the numbers here can be considered a maximum power requirement that may not be realized for any significant portion of the time the system is being used.

Although it is not clear from this table, IDC analysts generally assesses that most of the newer data centers in operation or those planned for the next few years will be able to offer an adequate power supply for these systems.

Only older sites, or those looking to expand their operation well into the next decade, will

require any significant new data center upgrades due to limitations in power or cooling

capabilities.

## Table 4

#### System Attributes: Power

| Computer Names             | Planned Delivery Date       | Planned Computer System<br>Power (MW) | Data Center Peak Power<br>(MW) |

|----------------------------|-----------------------------|---------------------------------------|--------------------------------|

| Sierra                     | 2017, 3Q                    | 10                                    | 30                             |

| Summit                     | 2017, 3Q                    | 13.3                                  | 25                             |

| Aurora                     | 2018, 4Q                    | 13                                    | 40                             |

| CORI                       | 2016, 4Q                    | <3.7                                  | 12.5+                          |

| Crossroads                 | 2020, 4Q                    | 18                                    | 25MW to 35 MW                  |

| NERSC-9                    | 2020, 4Q                    | 18                                    | 25MW to 35 MW                  |

| Cheyenne                   | 2017, 3Q                    | 1.75                                  | 8                              |

| TaihuLight                 | 2016<br>(2020, 4Q)          | 15.37                                 | 20-25                          |

| TianHe2 A                  | 2017 2Q or 3Q<br>(2020, 4Q) | 17.8+                                 | 20-25                          |

| Hazel Hen                  | 2015                        | 3.2                                   | 4                              |

| SuperMUC                   | 2015                        | 1.1                                   | 20                             |

| Piz Diant                  | 2016                        | 2.325                                 | 20                             |

| D-Wave                     | 2015                        | 25kw                                  | Very low, under a few MW       |

| UK Three System<br>Upgrade | 2018, 3Q                    | U/U/C                                 | U/U/C                          |

| CEA/Bull                   | 2020, 3Q                    | <20                                   | 50                             |

Source: IDC 2016

U/U/C = Uncertain/Unknown/Confidential

## System Attributes: MTBF Rates

As seen in table 5, few sites currently stress specific or hard requirements for MTBF rates. However, IDC analysts note that most pre-exascale designers are generally - and increasingly - concerned with

the large amount of advanced hardware and complex software that running these systems entails, and they are aggressively looking for ways to ensure that failures of these components, either hardware or software, do not significantly impact the ability of these systems to consistently execute some of their most demanding jobs.

- This issue is becoming increasingly more vexing as the overhead for preforming midcomputation checkpoints are increasingly an invasive, expensive, and performance limiting procedure.

- Hence, it is safe to conclude that designers of all of these system are acutely aware of reliability concerns for their system and do indeed have some metrics in mind for system reliability, but that in many cases that data is simply not publicly available.