### THE EUROPEAN APPROACH FOR EXSCALE AGES

### TOP10 OVER THE LAST 10 YEARS

|            | 2009 – Nov. | 2014 – Nov. | 2019 – Nov. | (Post)<br>Exascale |

|------------|-------------|-------------|-------------|--------------------|

| CPU only   | 9           | 5           | 2           | 0                  |

| CPU + ACC. | I           | 5           | 8           | 10                 |

### WHY? SOME OBVIOUS REASONS...

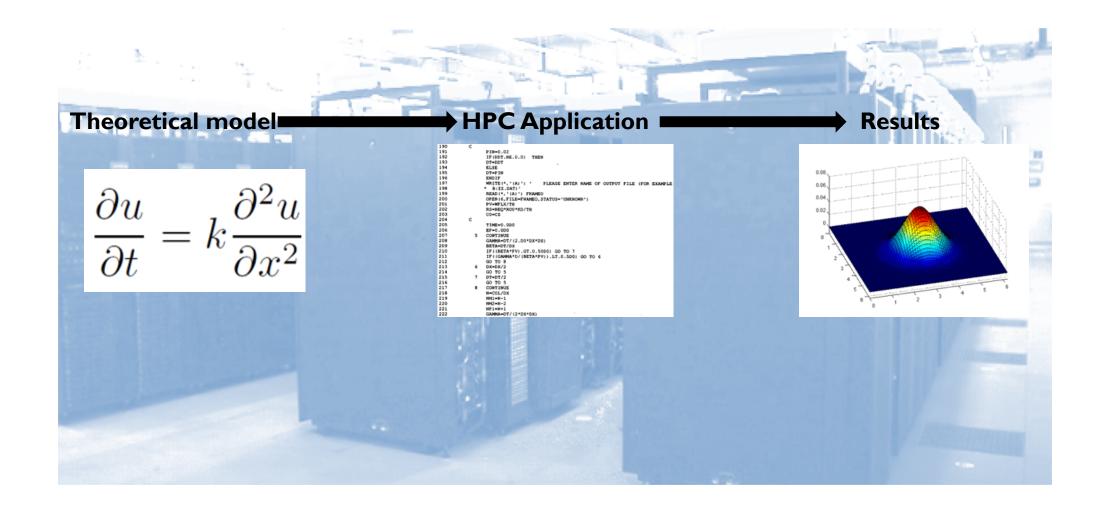

### HPC BEFORE ARTIFICIAL INTELLIGENCE

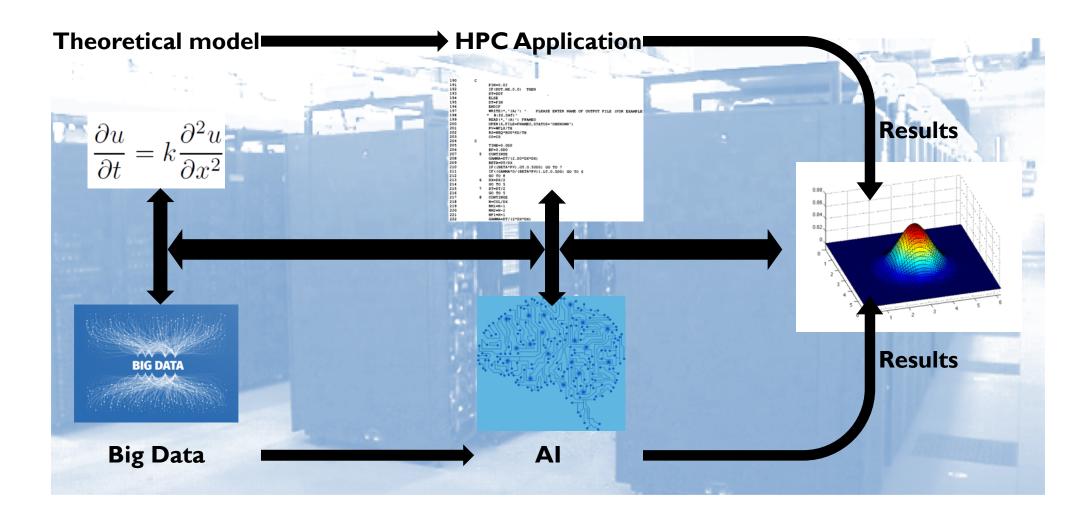

### HPC WITH ARTIFICIAL INTELLIGENCE

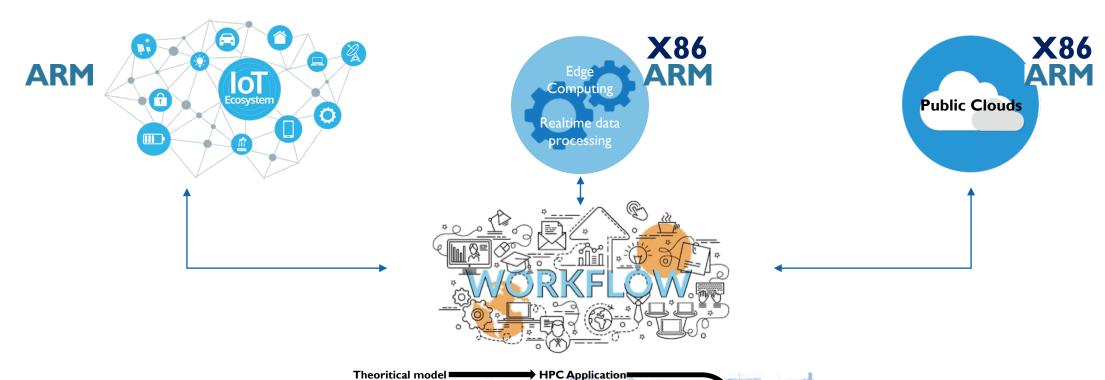

### HPC & AI AT EXASCALE: IT'S ALL ABOUT WORKFLOWS (1/2)

### HPC & AI AT EXASCALE: IT'S ALL ABOUT WORKFLOWS (2/2)

### HPC & AI AT EXASCALE: IT'S ALL ABOUT WORKFLOWS (2/2)

# THE DEVELOPER / USER STANDPOINT

### EVIDENCE: INTEL OVERALL STRATEGY IN HPC, CLOUD, EDGE

#### **Intel own accelerator developments:**

- GPU (Artic Sound)

- CSA

# Accelerator companies acquired by Intel or with intel in their Capital, in the last years:

- Altera

- Habana

- Mobileye

- <u>Untether AI</u>\* (Toronto, Ontario, Canada)

- SambaNova Systems\* (Palo Alto, California, U.S.)

- Zhuhai EEasy Technology Co. Ltd.\*

(Zhuhai, China)

- ...

# LESSONS LEARNED

#### PROFILE FOR EXASCALE SOLUTIONS

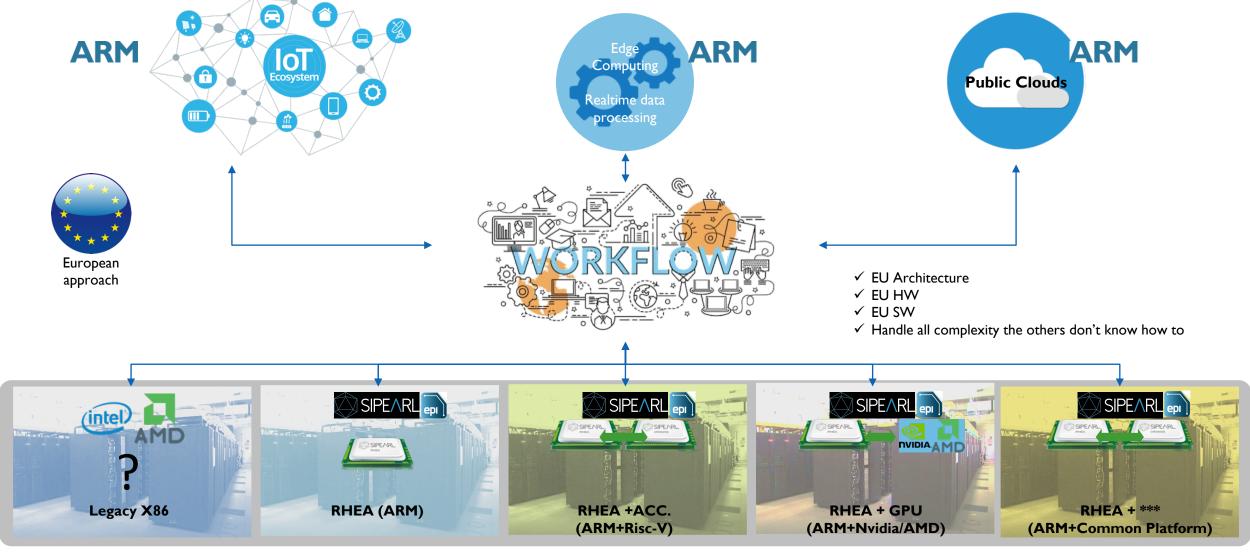

#### Main changes

- Holistic view of data from IoT to Supercomputers.

- Hybrid in-house / cloud

- Workflow everywhere

Modularity is a must have. One does not fit all

Several accelerators, typically one per module

Performance comes from accelerators

#### The CPU has to be well balanced

- peak performance is not important

- Agility (FP64 for HPC, BF16 for deep learning) is crucial

- Data transfer is crucial

- → Cover day to day needs and for all compute not fitting well in ACC

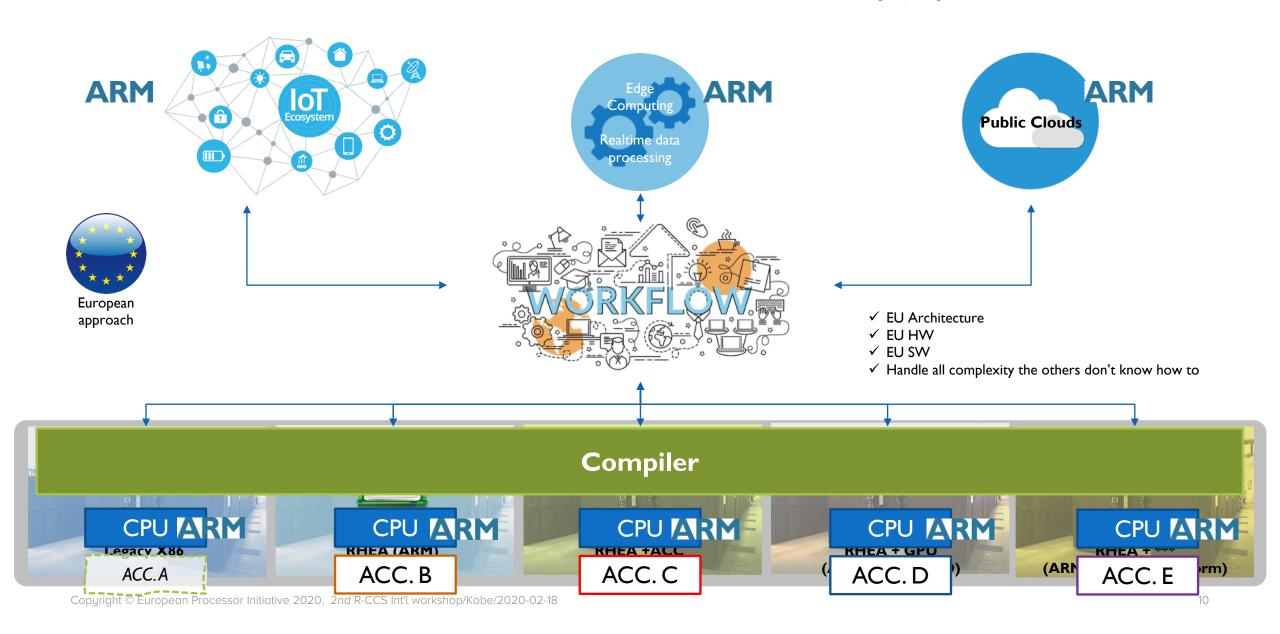

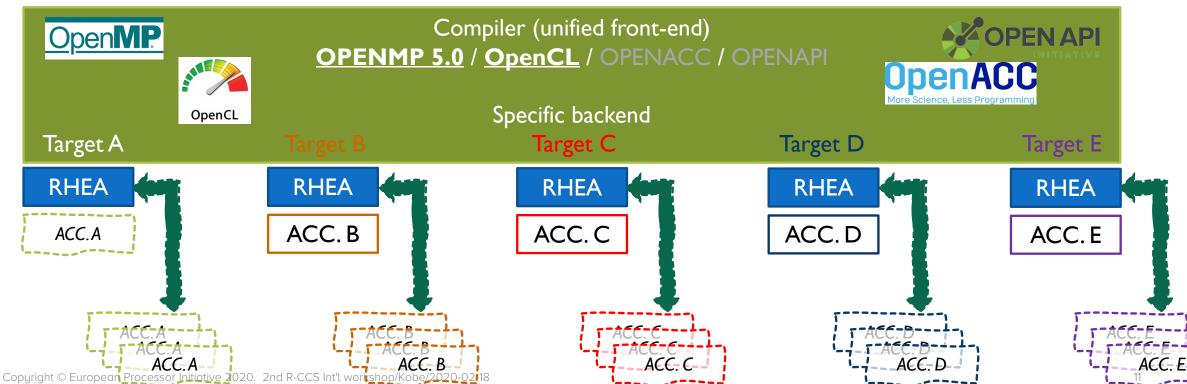

#### Keep overall architecture simple

→ one CPU to unify all accelerators

### Keep end user life simple

- I CPU only

- LLVM + GCC + OPENMP 5.0

- Keep it open!

### **TECHNOLOGY & ROADMAP**

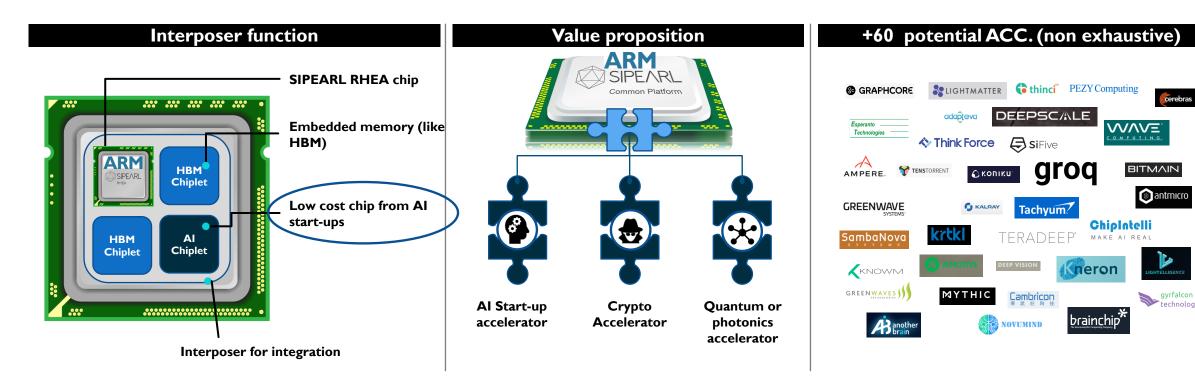

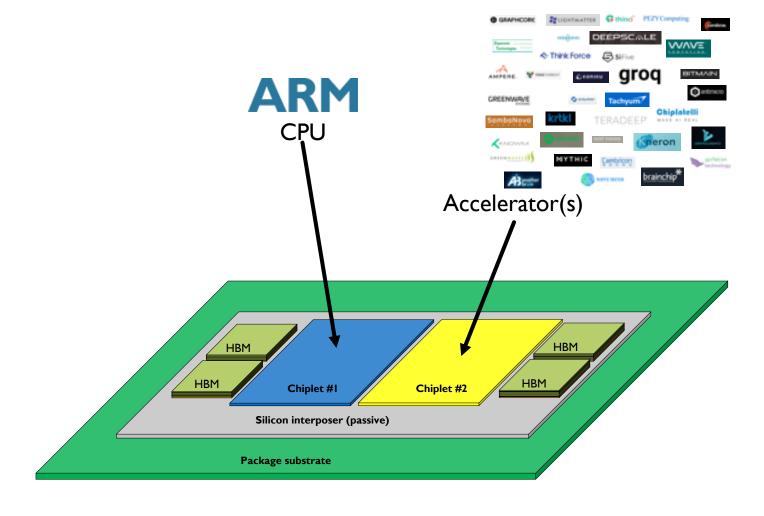

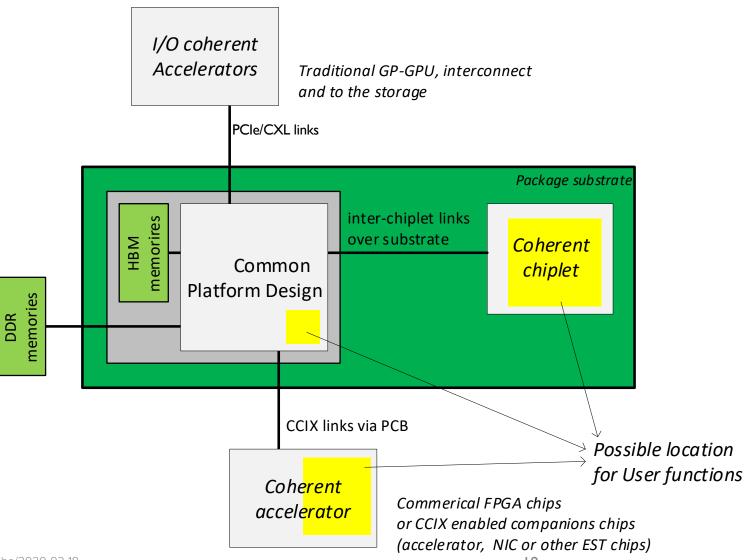

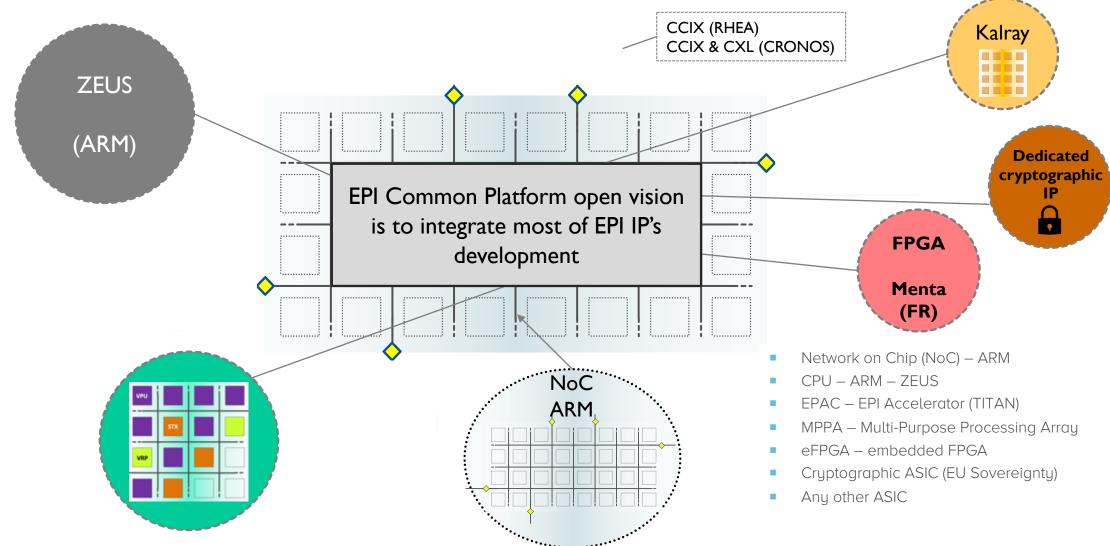

#### COMMON PLATFORM VISION: FEDERATE ACCELERATORS

# THE COMMON **OPEN** PLATFORM IS THE EUROPEAN STANDARD FOR MANAGING EXTREME SPECIALIZATION

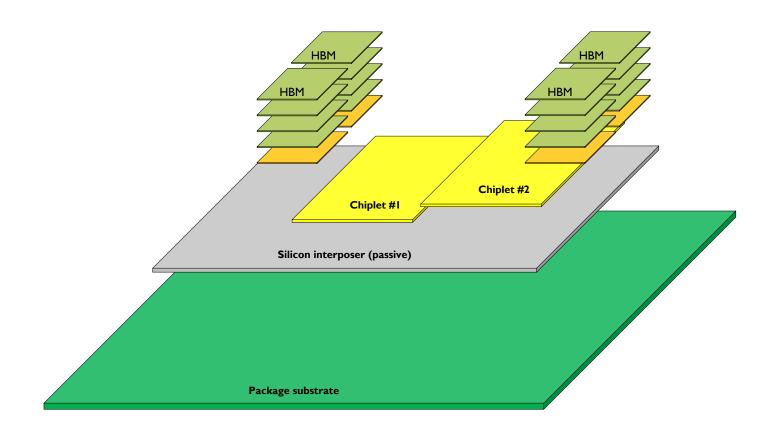

### CONCEPT OF COMMON PLATFORM: INTERPOSER & MULTI-CHIPLET

#### CONCEPT OF COMMON PLATFORM: INTERPOSER & MULTI-CHIPLET

### HETEROGENEOUS INTEGRATION

- Integrating customized functions at different levels

- EPI accelerator IPs today are integrated in Rhea design

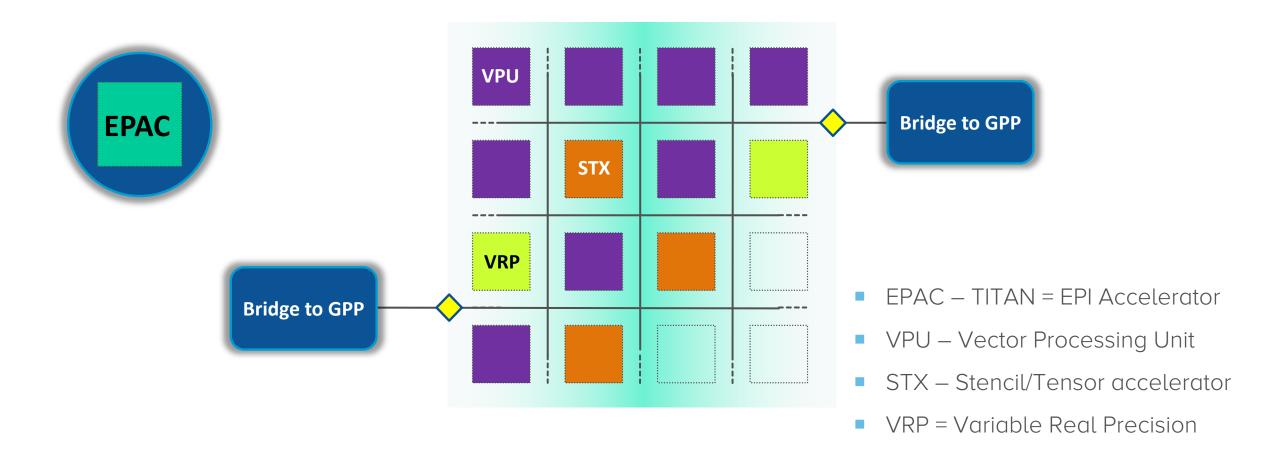

### GENERAL PURPOSE PROCESSOR (GPP) AND COMMON OPEN ARCHITECTURE

# CPU (RHEA) DESIGNS

- Multi-core Armv8.x processor for both computing and control flow

- Very high Byte/FLOP ratio

- EPI Accelerators work in I/O coherent mode and share the same memory view

- Coherent NoC with system level cache to keep the data local

- HBM2e, DDR5 and PCIe gen5

- High-speed links for SMP and for functional extensions

- Low voltage to improve the energy efficiency / N6 process

### EPAC - RISC-V ACCELERATOR FOUNDATIONS

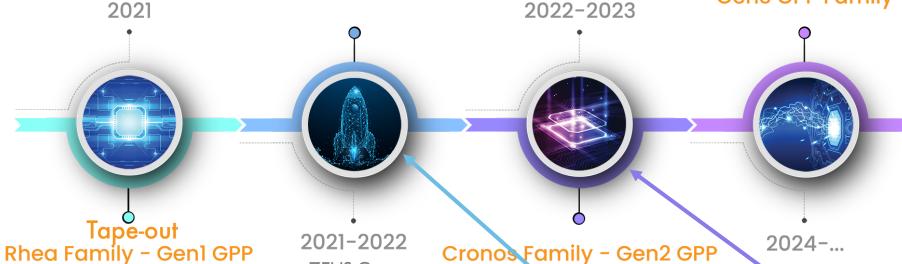

#### **ROADMAP**

#### EPI IP's Launch Pad

Pan European Research Platform for HPC and Al

**ZEUS** Core TITAN Acc. 5nm 2022-2023

Gen3 GPP Family

**EPI Common Platform** ARM & RISC-V **External IPs**

**HPC System PreExascale Automotive PoC**

**ZEUS** Core N6

**Test Platform**

SIPEARL

Cronos Family - Gen2 GPP

**EPI Common Platform** ARM & RISC-V

**HPC System Exascale Automotive CPU**

**EU Exascale Supercomputer** Edge-HPC (autonomous vehicle) with CRONOS & TITAN

<u> 2021 – H2</u>

E4 - PCle board (WS compatible) ATOS - BullxSequana Board with RHEA β version

Copyright © European Processor Initiative 2020. 2nd R-CCS Int'l work

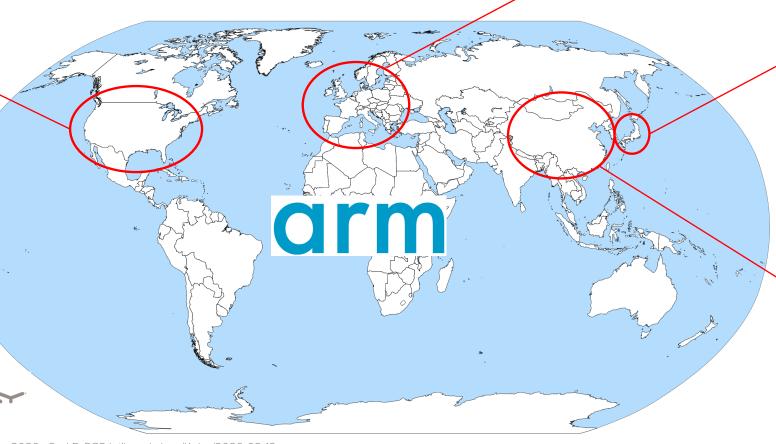

### **ARM WW HPC**

Upcoming CPU

manufacturer,

Server manufacturer,

system at CEA, UK,

MontBlanc, EPI

CPU

manufacturer,

2 server

manufacturers,

"Astra" system at

Sandia,

upcoming system

at Stony Brook

CPU & server manufacturer, upcoming "Fugaku" system

CPU & server manufacturer [geopolitical issues regarding the license]

### CONCLUSION

# EUROPEAN APPROACH FOR (POST) EXASCALE CHALLENGES

#### **Technology** Open Ecosystem (holistic) One CPU to rule all accelerators ARM from IoT to HPC ARM is the best choice: performances, Common Open platform GCC and LLVM openness, unique IoT to Supercomputer OPENMP 5 Open programming model ecosystem Aim open hardware **OPENCL** Chiplet based approach Common Open Platform

### THANK YOU FOR YOUR ATTENTION

- www.european-processor-initiative.eu

- @EuProcessor

- in European Processor Initiative

- European Processor Initiative